如何制作一個簡單的16位CPU,首先我們要明確CPU是做什么的,想必各位都比我清楚,百度的資料也很全。。。。。

如果想要制作一個CPU,首先得明白下計算機的組成結構(或者計算機的替代品,因為并不是只有計算機有CPU,現在的電子產品都很先進,很多設備例如手機、洗衣機甚至電視和你家的汽車上面都得裝一個CPU),數字電路基礎,還最好有點編程的基礎(當然,沒有也沒關系,這些知識都很容易獲得,各種書上面都會提到,并且在接下來的過程中我會提到這些知識)

我們要實現的是一個RISC指令集的CPU,并且我們最后要自己為這個CPU設計指令并且編碼。

首先我們來聽個故事,關于CPU的誕生的故事:

日本客戶希望英特爾幫助他們設計和生產八種專用集成電路芯片,用于實現桌面計算器。英特爾的工程師發現這樣做有兩個很大的問題。第一,英特爾已經在全力開發三種內存芯片了,沒有人力再設計八種新的芯片。第二,用八種芯片實現計算器,將大大超出預算成本。英特爾的一個名叫特德.霍夫(Ted Hoff)的工程師仔細分析了日本同行的設計,他發現了一個現象。這八塊芯片各實現一種特定的功能。當用戶使用計算器時,這些功能并不是同時都需要的。比如,如果用戶需要計算100個數的和,他會重復地輸入一個數,再做一次加法,一共做100次,最后再打印出來。負責輸入、加法和打印的電路并不同時工作。 這樣,當一塊芯片在工作時,其他芯片可能是空閑的。

霍夫有了一個想法:為什么不能用一塊通用的芯片加上程序來實現幾塊芯片的功能呢?當需要某種功能時,只需要把實現該功能的一段程序代碼(稱為子程序)加載到通用芯片上,其功能與專用芯片會完全一樣。

經過幾天的思考后,霍夫畫出了計算器的新的體系結構圖,其中包含4塊芯片:一塊通用處理器芯片,實現所有的計算和控制功能;一塊可讀寫內存(RAM)芯片, 用來存放數據;一塊只讀內存(ROM)芯片,用來存放程序;一塊輸入輸出芯片,實現鍵入數據和操作命令、打印結果等等功能。

看完這個故事后,可以總結:CPU是一種用來代替專用集成電路的器件(這只是我的理解,不同人有不同理解,這個就智者見智了,我在接下來的例子中也會說明我的想法)。

然后考慮如下這個例子:

例1-1:

mov eax,0

repeat:inc eax

jmp repeat

例1-2:

int main()

int i = 0;

while(1)

i++;

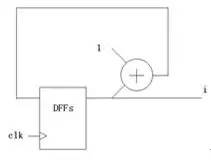

例1-3:

可以看到,以上三個例子都產生了一個從0不斷增加的序列,而且前兩個例子會一直加到溢出又從0開始(這個取決于計算機的字長也就是多少位的CPU,eax是 32位寄存器所以必然是加到然后回0,而后面那個c程序則看不同編譯器和不同平臺不一樣),后面那個例子則看你用的是什么樣的加法器和多少個D觸發器。

那問題就來了,我假設要一個遞減的序列怎么辦呢?前兩個例子很好解釋,我直接改代碼不就得了:

例2-1:

mov eax,0

repeat:dec eax

jmp repeat

例2-2:

int main()

int i = 0;

while(1)

i--;

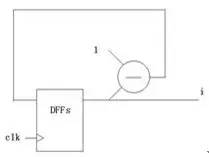

你只需要輕輕敲擊鍵盤,修改了代碼之后,它就會如你所愿的執行。但是后面那個例子怎么辦呢?可能你已經想到辦法了:如例2-3所示。

例2-3:

問題就來了,你在鍵盤上敲兩下可不能改變實際電路!上面(例1-3)中是個加法器,但是跑到這里卻變成了減法器(例2-3)!

這樣的話,你就得再做一個電路,一個用來算加法,一個用來算減法,可是兩個電路代表你得用更多的電路和芯片,你花的錢就得更多,要是你不能同時使用這兩個電路你就花了兩份錢卻只干了一件事!

這個問題能被解決嗎?答案是能!

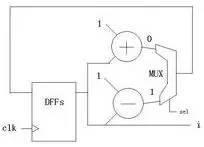

請看例3:

這個例子中使用了一個加法器一個減法器,沒比上面的電路省(顯然。。。。難道你想用減法器做加法器的功能?不可能吧!當然,加上一個負數的補碼確實就是減去 一個數,但是這里先不考慮這種問題),多了一組多路器,少了一組D觸發器。總的來說,優勢還是明顯的(兩塊電路板和一塊電路板的差別)。而sel信號就是用來選擇的(0是遞增,1是遞減)。

如果我們把sel信號看做“程序”的話,這個電路就像一個“CPU”能根據“程序”執行不同的“操作”,這樣的話,通過“程序”(sel信號),這個電路就能夠實現復用。

根據上面的結論,我認為(僅僅是個人認為啊~):程序就是硬件電路的延伸!

而CPU的基本思想,我認為就是這樣的。

接下來我們就分析CPU的結構和各個部件,然后實現這個CPU。

什么是單周期CPU,什么是多周期CPU,什么是RISC,什么是CISC

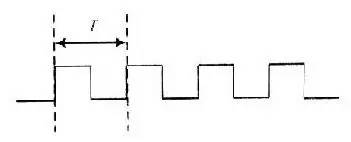

首先大家得有時鐘的概念:這個問題不好解釋 啊。。。。。。可以理解為家里面的機械鐘,上上電池之后就會滴答滴答走,而它“滴答滴答”的速度就是頻率,滴答一下用的時間就是周期,而人的工作,下班, 吃飯和學習娛樂都是按照時鐘的指示來進行的(熬夜的網癮少年不算),一般來說,時鐘信號都是由晶體振蕩器產生的,0101交替的信號(低電平和高電平)。

數字電路都需要一個“時鐘”來驅動,就像演奏交響樂的時候需要一個指揮家在前面指揮一樣,所有的人都會跟著指揮的拍子來演奏,就像數字電路中所有的部件都會跟著時鐘節拍工作一樣。

如下是一個理想的時鐘信號:(注意是理想的)。

當然,實際的時鐘信號可能遠沒有這么理想,可能上升沿是斜的,而且占空比也可能不是50%,有抖動,有偏移(相對于兩個器件),可能因為導線的寄生電容效應變得走形。

上面那段如果沒聽懂也沒關系~~~反正就是告訴你,實際的時鐘信號測出來肯定沒這么標準。

而 cpu的工作頻率,是外頻與倍頻的積(cpu究竟怎么算頻率,其實這個我也不太清楚呵呵),因為cpu是通過外部的晶振產生一個時鐘信號,然后再通過內部 的電路(鎖相環),倍頻至需要的頻率。當然,有人問,為什么要這么麻煩呢?直接在電路外邊做個時鐘晶振能產生那么高的時鐘信號就可以了嘛,這個是可以的, 在某些簡單的系統上(例如51單片姬)就是這樣的,但是計算姬的cpu比較復雜,因為一些原因所以必須要做到cpu內。

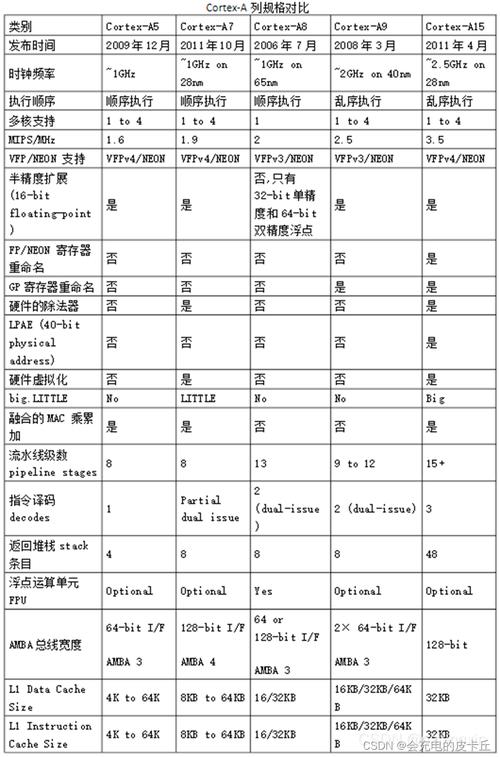

下面簡單說一下CPU的兩種指令集:CISC和RISC。

說下我的看法(個人看法,如有錯誤還請高手指正):

RISC是Reduced Set ,精簡指令集計算機,典型例子是MIPS處理器。

CISC 是Complex Set Compute,復雜指令集計算機,典型例子是x86系列處理器(當然現在的x86指令還是當初cisc的指令,但是實際處理器的結構都已經變成了 risc結構了,risc的結構實現流水線等特性比較容易,在計算機前的你如果用的是intel某系列的處理器,則它使用的指令集看上去還是像cisc的 指令,但是實際上你的cpu的結構已經是risc的了)。

一般CISC的處理器需要用微指令配合運行,而RISC全部是通過硬連線實現的, 也就是說,當cisc的處理器在執行你的程序前,還得先從另外一個rom里面讀出一些數據來“指導”處理器怎么處理你的命令,所以cisc效率比較低,而 risc是完全通過部件和部件之間的連接實現某種功能,極大的提高了工作效率,而且為流水線結構的出現提供了基礎。cisc的寄存器數量較少,指令能夠實 現一些比較特殊的功能,例如8086的一些寄存器:

ax,bx,cx,dx,si,di等;段寄存器有:cs,ds,es,ss等。相對的指令功能比較特殊,例如xlat將bx中的值作為基地址,al中的值作為偏移,在內存中尋址到的數據送到al當中(以ds為段寄存器)

而risc的處理器則通用寄存器比較多,而指令的功能可以稍微弱一點,例如:以nios嵌入式處理器來說明,nios處理器有32個通用寄存器(r0~r31),而指令功能相對x86的弱一些,而且x86進行內存訪問是直接使用mov指令,nios處理器讀內存用的是load,寫內存用的是store,

二者響應中斷的方式也不一樣,舉一個典型的例子,x86的處理器將中斷向量表放在了內存的最低地址(0-1023,每個中斷向量占四個字節),能容納256 個中斷(以實模式的8086舉例)響應中斷時,將中斷號對應的地址上的cs和ip的值裝入到cs和ip寄存器而將原來的地址保存,并且保存狀態寄存器然后 進入中斷處理,而risc則擁有一個共同的中斷響應函數,這個函數會根據中斷號找到程序向系統注冊的函數的地址,并且調用這個函數。一般來說而是用的 cisc指令的長度是不定的,例如x86的xor ax,bx對應機器碼是0x31d8、而push ax是0x50、pop cx是0x59。而risc的指令確是定長的,例如32位。

如果還有不清楚的。。。。。自行百度,要理解這些概念需要一點時間。

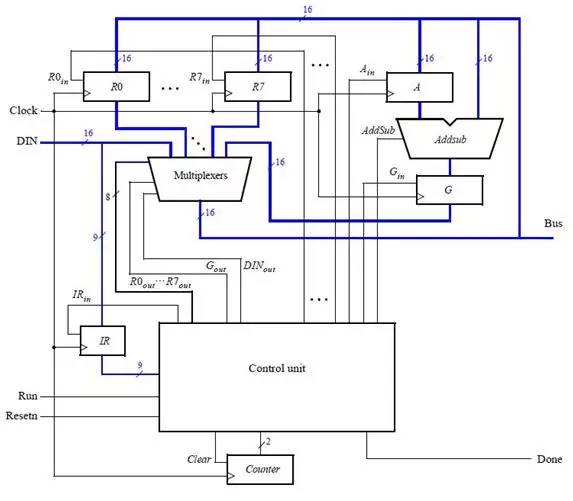

一個CPU的基本結構以及必要組件

這個例子引用自DE2開發板套件帶的光盤上的Lab 9,我們從圖中可以看到,一個CPU包含了通用寄存器組R0~R7,一個ALU(算術邏輯單元),指令寄存器IR,控制器(一般這部分是一個有限狀態機或 者是用微指令實現),還有就是數據通路(圖中的連線)。當然真正的CPU不可能只包含這么一點點組件,這是一個模型CPU,也就是說只是說明CPU的原 理,真正復雜的CPU要涉及到很多復雜的結構和時序,例如虛擬模式需要使用一些特殊的寄存器、為了支持分頁需要使用頁表寄存器等,為了加速內存的訪問需要 使用TLB,加速數據和指令的訪問而使用data cache和 cache等等。。。。。當然,那都是后面該考慮的,所以我們先從這個簡單的部分開始講起。

例子中能實現如下指令:

mv指令將Ry的數據轉移到Rx中,mvi將立即數D轉移到Rx當中,add將Rx和Ry的和放到Rx中,sub同上,不過執行的是減法。

首先來說明mv指令是如何執行的:mv指令將Ry的值移入Rx寄存器當中,這兩個寄存器都是由一組D觸發器構成,而D觸發器的個數取決于寄存器的寬度,就像 32位機、64位機這樣,那他們的寄存器使用的D觸發器的個數就是不一樣的。當執行mv rx,ry時,中間的多路器(圖中最大的那個)選通Ry,讓Ry寄存器驅動總線,這個時候Bus上的信號就是Ry的值;然后再看到 R0~R7上分別有R0in~R7in信號,這個信號是使能信號,當這個信號有效時,在上升沿此觸發器會將din的數據輸入,所以說到這里大家一定想到 了,這個時候Rx觸發器上的Din信號就會變為有效,這樣過了一個時鐘周期后Ry的值就被送到了Rx當中。

與mv指令類似,mvi指令也將一個數據送入Rx當中,只不過這次的數據存在指令當中,是立即數,所以Rx的Din信號會變為有效,而多路器會選擇IR中的數據,因為mvi指令的立即數存在指令當中。并且進行一定處理,例如擴展等。

add 指令會讓多路器先選擇Rx,然后Ain信號有效,這樣一個時鐘周期后,Rx數據被送入Alu的A寄存器當中,這時多路器選擇Ry,addsub信號為 add以指示ALU進行加法操作,Gin有效讓G寄存器存放運算結果,然后再過一個時鐘周期G當中的數據就是Rx與Ry的和,這時多路器再選擇 Gin,Rx的Din有效,過了一個時鐘周期后數據就被存放到Rx當中了。

sub的過程與add差不多,不過addsub信號是sub指示ALU進行減法。

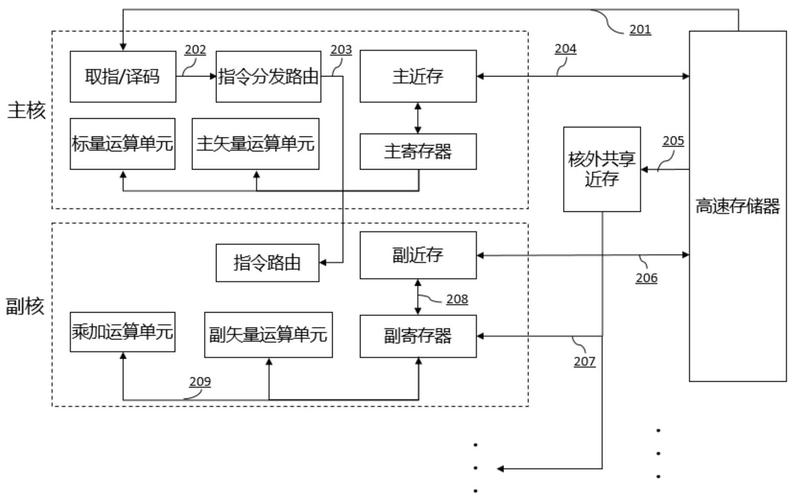

我做的CPU模型

下面我就將我做的CPU模型的RTL網表發出來,代碼我會上傳的,但是這個還只能進行仿真,因為設計 的時候理念有問題,出現了異步設計,而且出現了將狀態機的輸出作為另一個器件的時鐘端的錯誤,所以這個模型只能用于仿真。我用的 pro綜合出的RTL,而狀態轉移圖是用的Quartus的FSM Viewer截下來的。

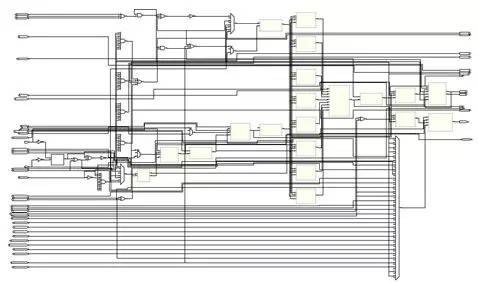

首先是整個系統的概覽:

這個比上面的那個簡單模型復雜多了吧!但是別擔心,其實這個只是上面的那個CPU變得稍微復雜了一點,這個和上面那個不同的地方還有:這個CPU是一個多周期CPU而上面的Lab 是一個單周期的CPU

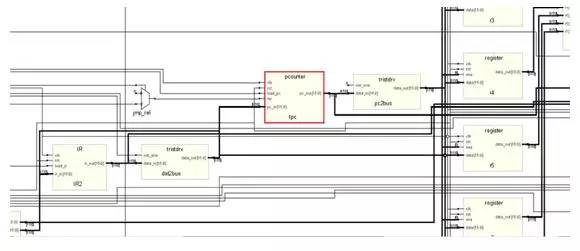

下圖是程序計數器(PC),也就是常見x86處理器里面的ip( ):

紅色部分就是pc了,后面是一個三態橋,連接到了總線上面,這里的數據有時候是要送到地址總線,用于尋內存中的數據,以便完成 Fetch過程。有時候又要送到通用寄存器的數據端,用于將pc的值送到其他寄存器。

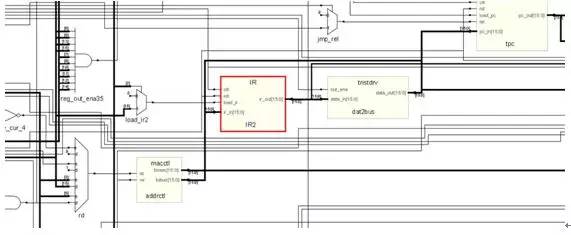

下面這個是IR( ),這個是多周期處理器的典型特征,因為處理器在第一個周期里面將機器碼從內存取出,然后存放到這個寄存器里面,后面的幾個狀態都是通過這個寄存器里面的數據作為指示執行操作的。

下面介紹一下ALU,ALU是 Logic Unit,即算術邏輯單元,這個裝置的作用是進行算術操作和邏輯操作。典型的算術操作例

如:1+1=2,11x23=253,而典型的邏輯操作例如:1 and 1=1,0 or 0 = 0,1